18329 - Endpoint for PCI Express - What clock frequency must be used when implementing a PCI Express solution in a Xilinx device?

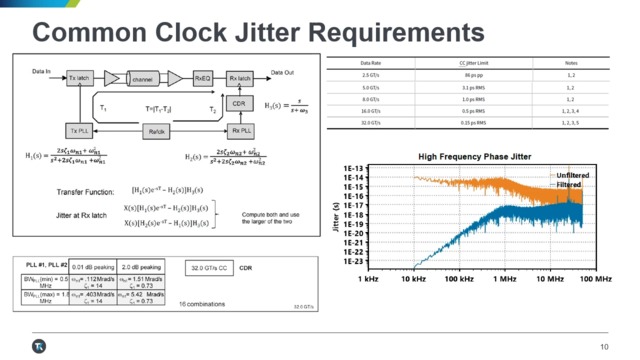

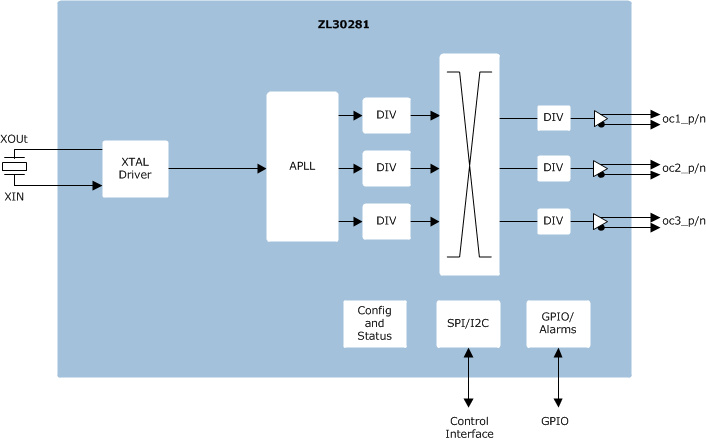

Timing is Everything: How to optimize clock distribution in PCIe applications - Analog - Technical articles - TI E2E support forums

Timing is Everything: How to optimize clock distribution in PCIe applications - Analog - Technical articles - TI E2E support forums

.jpg)